栏目导航

高速操控计划LED显现屏电路图及原理

文章出处:行业新闻 发表时间:2024-10-20 23:41:38

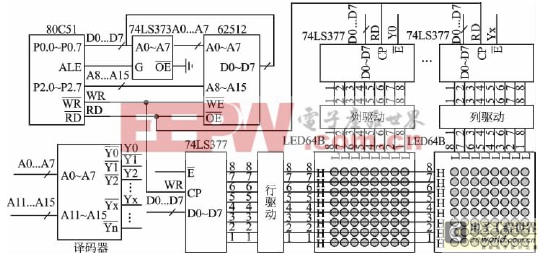

计划电路原理。选用MCS51系列单片机对来操控;随机存储器62512用作的数据存储器,存储待显现内容的字模数据;选用8行扫描办法,多片LED点阵片共用1组行驱动电路;每片LED点阵片都有一组列驱动电路,用

作为列驱动的锁存器,CPU经过并行总线给列驱动电路的锁存器写字模数据;地址译码电路,用于产生LED点阵片行驱动电路和列驱动电路的片选地址。

本计划的特色有两个: 榜首,尽管CPU仍是经过并行总线给列驱动电路的锁存器写字模数据,可是锁存器的锁存信号改用了CPU的操控信号RD,而不是惯例用法的WR;第二,地址译码电路确保了LED点阵片列驱动电路的片选地址和数据存储器的某一段的逻辑地址是堆叠的,而不是惯例用法,这两组地址有必要分隔。

由于上述电路的一些简略更改,单片机对LED显现屏的显现操控功率将产生显着的改变。详细工作进程如下: 假定数据指针DPTR中现已装入了数据存储器的地址,履行指令“MOVXA,@DPTR”。这条指令的功用是CPU按DPTR的指向从外部数据存储器中读字模数据,读到累加器A中;可是在本电路中,由于LED点阵片列驱动电路的片选地址和数据存储器的某一段的逻辑地址是堆叠的,也便是说,在履行指令“MOVXA,@DPTR”时,DPTR除了指向外部数据存储器的某个地址外,还选中了某一个LED点阵片列驱动电路的锁存器。假如此刻被选中的这个锁存器的锁存引脚正好有打入脉冲来到,那么锁存器也就将从外部数据存储器送出的字模数据锁住了。这个打入脉冲用的便是RD。RD是CPU在履行指令“MOVXA,@DPTR”时向外部数据存储器宣布的读操控信号。由于MCS51系列单片机的读操控信号RD和写操控信号WR的时序完全相同[2],RD替代WR完结锁存功用,当然也就没什么悬念了。这条指令在履行时,在完结对数据存储器读的一起,又完结了对LED点阵片的写,因而加快了显现操控的进程。

前面讲过,并行总线次向LED点阵片的列驱动电路的锁存器写字模数据的程序进程,大约需求十几μs;而现在只需4 μs,快多了,由于现在完结1次向LED点阵片的列驱动电路的锁存器写字模数据的程序进程只需两步,首先给数据指针DPTR赋有用地址,接着CPU按DPTR的指向从外部数据存储器中读字模数据,与此一起也将字模数据传给了LED点阵片列驱动电路的锁存器。2条指令,4个机器周期,4 μs。这儿要弥补阐明一点,在编制悉数LED点阵片列驱动电路的锁存器写字模数据的程序时,不要用循环指令,由于那样每次进程又得添加2 μs;要选用对LED点阵片逐片编程的办法,这样编出来的程序尽管占空间,但节省了时刻。用空间换时刻的规划办法,有时也是规划人员值得测验的一种办法。

本电路的行驱动锁存器的锁存操控,仍是用CPU的写操控信号WR,不作更改。行驱动锁存器的片选信号也来自地址译码电路。为了尽最大或许防止数据存储器和LED点阵片之间的彼此搅扰,与这组地址对应的数据存储器的这部分存储空间就不用它了。

地址译码电路的规划,应确保LED点阵片列驱动电路的片选地址和数据存储器的某一段的逻辑地址是堆叠的。详细规划举例如下:

假定某一块LED显现屏用了240片LED点阵片,可显现16×16的汉字60个,用1片MCS51系列单片机进行高速操控。这240片LED点阵片列驱动电路的片选地址就应有240个,地址译码电路一定要确保译码后的有用地址大于这个数量。图1中的地址译码电路,输入的地址信号是A0~A7和A11~A15,没有接入A8、A9、A10。用74LS138译码器,三级译码后可得到256根有用地址线H、0500H、0600H、0700H。第2根有用地址线H、0601H、0701H。……第256根有用地址线FFH、06FFH、07FFH。这256根有用地址线根给列驱动电路的片选地址,余下的给行驱动电路的片选地址;假如不够用,行驱动电路可考虑改为串行总线的办法来进行操控。上述剖析依据成果得出,1片LED点阵片的I/O接口地址和数据存储器的8个字节的地址建立了堆叠联系。这是由于每片LED点阵片都有8行,每行都对应1个字节的字模数据。

上述剖析成果还标明,悉数LED点阵片的I/O接口地址和数据存储器的0000H~07FFH地址段建立了映射联系。数据存储器0000H~07FFH中寄存的正好是一帧图画的悉数字模数据。